# XC61H Series

## Voltage Detector with Delay Circuit Built-In

### **■**GENERAL DESCRIPTION

The XC61H series is a highly accurate, low power consumption CMOS voltage detector with a delay circuit. Detect voltage is accurate with minimal temperature drift. Output configurations are available in both CMOS and N-channel open drain. Since the full delay circuit is built-in, an external delay-time capacitor is not necessary so that high density mounting is possible.

#### ■APPLICATIONS

- Microprocessor reset circuitry

- System battery life and charge voltage monitors

- Memory battery back-up circuits

- Power-on reset circuits

- Power failure detection

- Delay circuitry

#### **■**FEATURES

**Detect Voltage Accuracy** : ± 2%

**Low Power Consumption** :  $1.0\mu A(TYP.)[V_{IN}=2.0V]$

**Detect Voltage Range** : 1.6V ~ 6.0V (0.1V increments)

**Operating Voltage Range** : 0.7V ~ 10.0V **Detect Voltage Temperature Characteristics**

: ±100ppm/°C(TYP.)

Built-In Release Delay time: 1ms (MIN.)

50ms (MIN.) 80ms (MIN.)

**Output Configuration** : N-ch open drain or CMOS

: SOT-23

Environmentally Friendly : EU RoHS Compliant, Pb Free

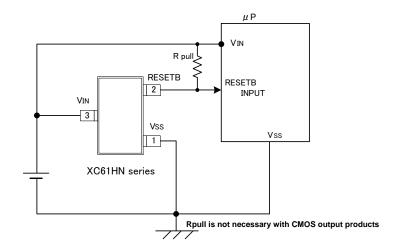

## ■TYPICAL APPLICATION CIRCUITS ■TYPICAL PERFORMANCE

# CHARACTERISTICS

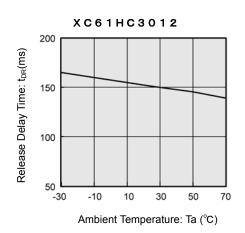

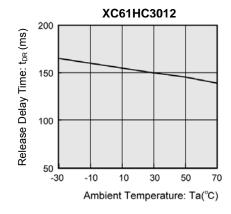

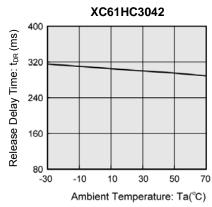

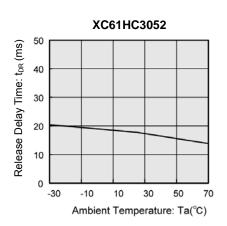

● Release Delay Time (t<sub>DR</sub>) vs. Ambient Temperature

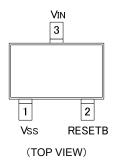

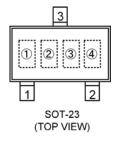

#### **■ PIN CONFIGURATION**

#### ■PIN ASSIGNMENT

| PIN NUMBER | PIN NAME        | FUNCTION             |  |  |

|------------|-----------------|----------------------|--|--|

| SOT-23     | FININAIVIE      | FUNCTION             |  |  |

| 1          | V <sub>SS</sub> | Ground               |  |  |

| 2          | RESETB          | Output               |  |  |

| 3          | V <sub>IN</sub> | Supply Voltage Input |  |  |

## **■PRODUCT CLASSIFICATION**

Ordering Information

XC61H 1234567-8(\*1)

| DESIGNATOR                           | ITEM                              | SYMBOL  | DESCRIPTION            |  |

|--------------------------------------|-----------------------------------|---------|------------------------|--|

| <b>3</b>                             | Output Configuration              | С       | CMOS output            |  |

| 1                                    |                                   | N       | N-ch open drain output |  |

| 23                                   | Detect Voltage (V <sub>DF</sub> ) | 16 ~ 60 | e.g. 2.5V → ②2 , ③5    |  |

|                                      |                                   | 1       | 50ms ~ 200ms           |  |

| 4                                    | Release Delay Time                | 4       | 80ms ~ 400ms           |  |

|                                      |                                   | 5       | 1ms ~ 50ms             |  |

| 5                                    | Detect Accuracy                   | 2       | ± 2.0% <sup>(*2)</sup> |  |

| <b>6</b> 7- <b>8</b> <sup>(*1)</sup> | Package<br>(Oder Unit)            | MR-G    | SOT-23 (3000/Reel)     |  |

<sup>(\*1)</sup> The "-G" suffix indicates that the products are Halogen and Antimony free as well as being fully RoHS compliant.

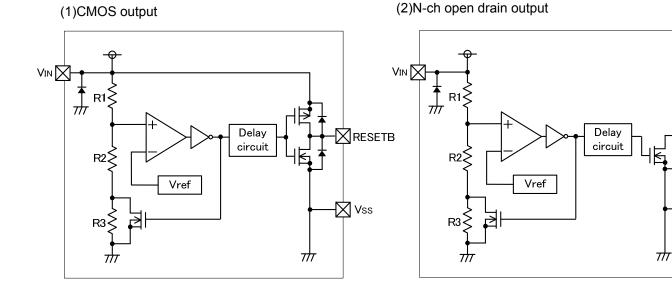

## **■BLOCK DIAGRAMS**

RESETB

Vss

<sup>(\*2)</sup> No parts are available with an accuracy of ± 1%

## ■ ABSOLUTE MAXIMUM RATINGS

Ta=25°C

| PARAMETER                   |                 | SYMBOL           | RATINGS                                    | UNITS |  |

|-----------------------------|-----------------|------------------|--------------------------------------------|-------|--|

| Input Voltage               |                 | $V_{IN}$         | 12.0                                       | V     |  |

| Output Current              |                 | I <sub>OUT</sub> | 50                                         | mA    |  |

| Output Voltage              | CMOS            | RESTB            | V <sub>SS</sub> -0.3 ~V <sub>IN</sub> +0.3 | V     |  |

|                             | N-ch open drain | KESIB            | V <sub>SS</sub> -0.3 ~ 12                  |       |  |

| Power Dissipation SOT-23    |                 | Pd               | 250                                        | mW    |  |

| Operating Temperature Range |                 | Topr             | -30~+80                                    | °C    |  |

| Storage Temperature Range   |                 | Tstg             | -40 <b>~</b> +125                          | °C    |  |

## **■**ELECTRICAL CHARACTERISTICS

Ta = 25°C

| PAR                                           | AMETER                                        | SYMBOL                             | CONDITIONS                                      |                        | MIN.                         | TYP.                      | MAX.                         | UNITS  | CIRCUIT |

|-----------------------------------------------|-----------------------------------------------|------------------------------------|-------------------------------------------------|------------------------|------------------------------|---------------------------|------------------------------|--------|---------|

| Dete                                          | ect Voltage                                   | $V_{DF}$                           |                                                 |                        | V <sub>DF(T)</sub><br>x 0.98 | $V_{DF(T)}$               | V <sub>DF(T)</sub><br>x 1.02 | V      | 1       |

| Hyste                                         | resis Width                                   | V <sub>HYS</sub>                   |                                                 |                        | V <sub>DF</sub> x 0.02       | V <sub>DF</sub><br>x 0.05 | V <sub>DF</sub> x 0.08       | V      | 1       |

|                                               |                                               |                                    |                                                 | V <sub>IN</sub> = 1.5V | -                            | 0.9                       | 2.6                          | -      |         |

|                                               |                                               |                                    |                                                 | V <sub>IN</sub> = 2.0V | -                            | 1.0                       | 3.0                          |        |         |

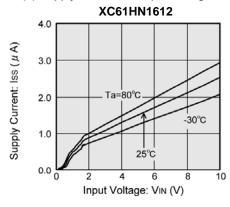

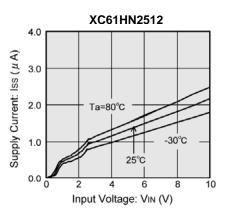

| Supply                                        | y Current (*1)                                | I <sub>SS</sub>                    |                                                 | V <sub>IN</sub> = 3.0V | -                            | 1.3                       | 3.4                          | μΑ     | 2       |

|                                               |                                               |                                    |                                                 | $V_{IN} = 4.0V$        | -                            | 1.6                       | 3.8                          |        |         |

|                                               |                                               |                                    |                                                 | V <sub>IN</sub> = 5.0V | -                            | 2.0                       | 4.2                          |        |         |

| Opera                                         | ting Voltage                                  | $V_{IN}$                           | V <sub>DF</sub> =1.6V∼6.0V                      |                        | 0.7                          | -                         | 10.0                         | V      | 1       |

|                                               |                                               |                                    | -                                               | $V_{IN} = 1.0V$        | 1.0                          | 2.2                       | -                            |        |         |

|                                               |                                               | $I_{OUT}$ N-ch, $V_{DS} = 0.5V$    |                                                 | V <sub>IN</sub> = 2.0V | 3.0                          | 7.7                       | -                            |        |         |

|                                               |                                               |                                    | V <sub>IN</sub> = 3.0V                          | 5.0                    | 10.1                         | -                         | ]                            | 3      |         |

| Outp                                          | out Current                                   |                                    |                                                 | V <sub>IN</sub> = 4.0V | 6.0                          | 11.5                      | -                            | mA     |         |

|                                               |                                               |                                    |                                                 | V <sub>IN</sub> = 5.0V | 7.0                          | 13.0                      | -                            |        |         |

|                                               |                                               |                                    | P-ch, V <sub>DS</sub> =2.1V<br>(CMOS Output)    | V <sub>IN</sub> = 8.0V |                              | -10.0                     | -2.0                         |        | 4       |

| Leakage<br>Current                            | CMOS Output                                   | I <sub>LEAK</sub>                  | V <sub>IN</sub> =10.0V, V <sub>OUT</sub> =10.0V |                        | -                            | 0.01                      | -                            | μΑ     | 3       |

| Current                                       | Nch Open Drain                                |                                    |                                                 |                        | -                            | 0.01                      | 0.1                          |        |         |

|                                               | Detect Voltage<br>Temperature Characteristics |                                    |                                                 |                        | -                            | ±100                      | -                            | ppm/°C | -       |

| Release                                       | a Dalay Tima                                  |                                    |                                                 |                        | 50                           | -                         | 200                          |        |         |

| Release Delay Time<br>(VDR → RESEB inversion) |                                               | t <sub>DR</sub> Vin changes from 0 |                                                 | 0.6V to 10V            | 80                           | -                         | 400                          | ms     | 5       |

| (ADIC VIC                                     | (VDR - RESEB IIIVEISIOII)                     |                                    |                                                 |                        | 1                            | -                         | 50                           |        |         |

VDF (T) is nominal detect voltage value Release Voltage: VDR = VDF + VHYS

<sup>(\*1)</sup> The supply current during power-start until output being stable (during release operation) is 2  $\mu$  A greater with comparison to the period after the completion of release operation because of the shoot-through current in delay current.

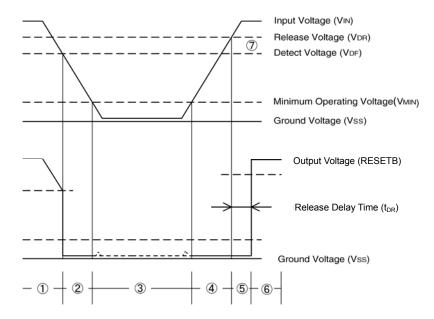

## **■**OPERATIONAL EXPLANATION

#### CMOS output

- ① An input voltage V<sub>IN</sub> starts higher than the release voltage V<sub>DR</sub>. Then, V<sub>IN</sub> voltage will gradually fall. When V<sub>IN</sub> voltage is higher than detect voltage V<sub>DF</sub>, output voltage RESETB is equal to the V<sub>IN</sub> voltage.

- \*Note that high impedance exists at RESETB with the N-channel open drain configuration. If the RESETB pin is pulled up, RESETB will be equal to the pull up voltage.

- 2) When VIN falls below VDF, RESETB will be equal to ground voltage Vss level (detect state).

- \* Note that this also applies to N-channel open drain configurations.

- When VIN falls to a level below that of the minimum operating voltage VMIN, output will become unstable.

\*When the output pin is generally pulled up with N-channel open drain configurations, output will be equal to pull up voltage.

- When Vin rises above the Vss level (excepting levels lower than minimum operating voltage), RESETB will be equal to Vss until Vin reaches the VDR level.

- S Although Vin will rise to a level higher than VDR, RESETB maintains ground voltage level via the delay circuit.

- After taking a release delay time, VIN voltage will be output at the RESETB pin.

\*High impedance exists with the N-channel open drain configuration and that voltage will be dependent on pull up.

#### Notes:

- 1. The difference between VDR and VDF represents the hysteresis width.

- 2. Release delay time ( $t_{DR}$ ) represents the time it takes until when VIN voltage appears at RESETB pin once the input voltage has exceeded the VDR level.

### Timing Chart

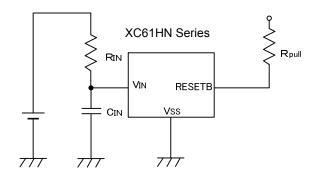

#### ■NOTES ON USE

- 1. Please use this IC within the stated maximum ratings. The IC is liable to malfunction should the ratings be exceeded.

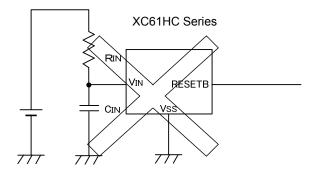

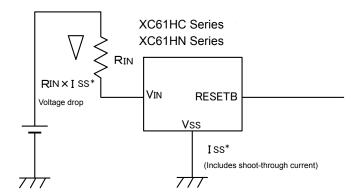

- 2. When a resistor is connected between the VIN pin and the input with CMOS output configurations, irregular oscillation may occur as a result of voltage drops at RIN if load current (IOUT) exists. It is therefore recommend that no resistor be added. (refer to Figure 1 below)

- 3. When a resistor is connected between the Vin pin and the input with CMOS output configurations, irrespective of N-ch output configurations, oscillation may occur as a result of shoot-through current at the time of voltage release even if load current (Iout) does not exist. (refer to Figure 1 below)

- 4. By connecting a resistor between the VIN pin and the input, detect and release voltages will rise as a result of the IC's supply current flowing through the VIN pin.

- 5. If a resistor (RIN) must be used, then please use with as small a level of input impedance as possible in order to control the occurrences of oscillation as described above.

- Further, please ensure that RIN is less than  $10k\Omega$  and that CIN is more than  $0.1 \mu$  F (Figure 1). In such cases, detect and release voltages will rise due to voltage drops at RIN brought about by the IC's supply current.

- 6. Depending on circuit's operation, release delay time of this IC can be widely changed due to upper limits or lower limits of operational ambient temperature.

#### Irregular Oscillations

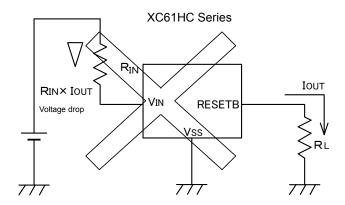

(1) Irregular oscillation as a result of output current with the CMOS output configuration:

When the voltage applied at IN rises, release operations commence and the detector's output voltage increases. Load current (IOUT) will flow through RL. Because a voltage drop (RIN x IOUT) is produced at the RIN resistor, located between the input (IN) and the VIN pin, the load current will flow via the IC's VIN pin. The voltage drop will also lead to a fall in the voltage level at the VIN pin. When the VIN pin voltage level falls below the detect voltage level, detect operations will commence. Following detect operations, load current flow will cease and since voltage drop at RIN will disappear, the voltage level at the VIN pin will rise and release operations will begin over again.

Irregular oscillation may occur with this "release - detect - release" repetition.

Further, this condition will also appear via means of a similar mechanism during detect operations.

(2) Irregular oscillation as a result of shoot-through current:

Since the XC61H series are CMOS ICs, shoot-through current will flow when the IC's internal circuit switching operates (during release and detect operations). Consequently, irregular oscillation is liable to occur during release voltage operations as a result of output current which is influenced by this shoot-through current (Figure 3).

Since hysteresis exists during detect operations, irregular oscillation is unlikely to occur.

Figure 1 Use of input resistor  $R_{\text{IN}}$

## ■NOTES ON USE

●Irregular Oscillations (Continued)

Figure 2 Irregular Oscillation by output current

Figure 3 Irregular Oscillation by shoot-through current

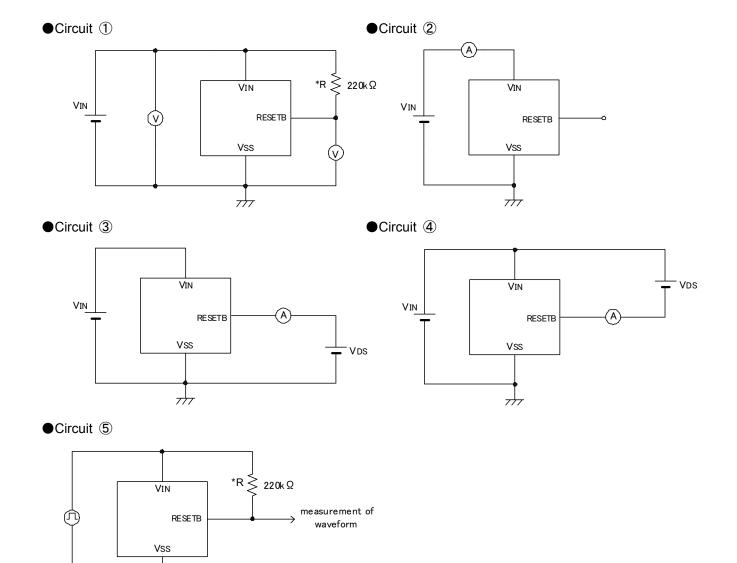

## **■**TEST CIRCUITS

\*R is not necessary with CMOS output products.

## **■**TYPICAL PERFORMANCE CHARACTERISTICS

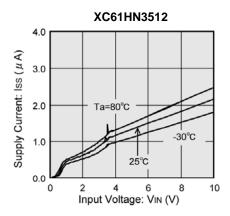

#### (1) Supply Current vs. Input Voltage

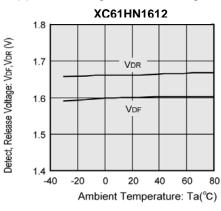

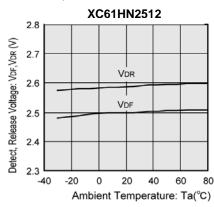

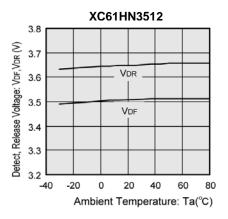

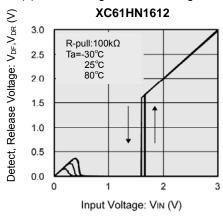

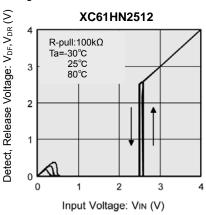

(2) Detect Voltage, Release Voltage vs. Ambient Temperature

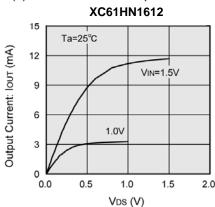

(3) Detect Voltage, Release Voltage vs. Input Voltage

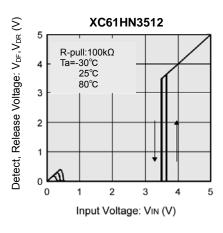

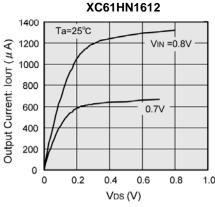

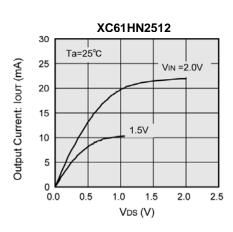

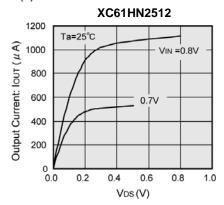

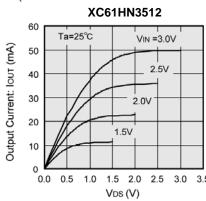

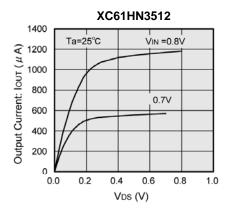

(4) N-Channel Driver Output Current vs. VDS

# ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

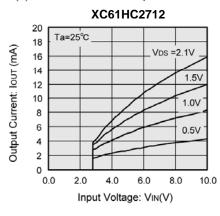

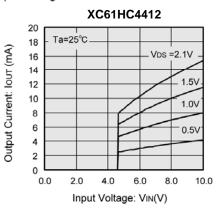

(4) N-Channel Driver Output Current vs. VDS (Continued)

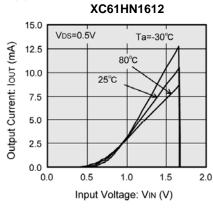

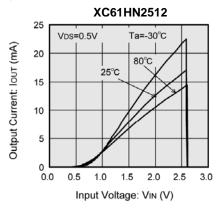

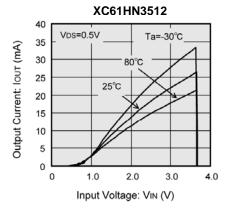

(5) N-Channel Driver Output Current vs. Input Voltage

(6) P-Channel Driver Output Current vs. Input Voltage

(7) Ambient Temperature vs. Release Delay Time (t<sub>DR</sub>)

# ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

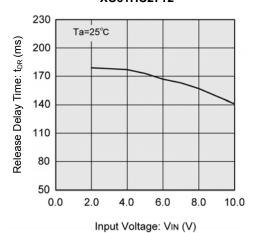

(8) Input Voltage vs. Release Delay Time (t<sub>DR</sub>)

#### XC61HC2712

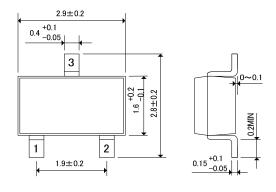

## **■**PACKAGING INFORMATION

#### ●SOT-23

(unit:mm)

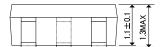

## **■**MARKING RULE

#### ●SOT-23

① represents product series

| MARK | PRODUCTS SERIES |

|------|-----------------|

| 8    | XC61H*****-G    |

2 standard : represents output configuration and integer number of detect voltage

CMOS output (XC61HC series)

| MARK | VOLTAGE<br>(V) |  |

|------|----------------|--|

| Α    | 1. X           |  |

| В    | 2. X           |  |

| С    | 3. X           |  |

| D    | 4. X           |  |

| E    | 5. X           |  |

| F    | 6. X           |  |

N-channel open drain (XC61HN series)

| MARK | VOLTAGE<br>(V) |

|------|----------------|

| Р    | 1. X           |

| R    | 2. X           |

| S    | 3. X           |

| Т    | 4. X           |

| U    | 5. X           |

| V    | 6. X           |

③ represents decimal number of detect voltage and delay time.

| DETECT         | MARK                                         |                                              |                                            |  |  |  |

|----------------|----------------------------------------------|----------------------------------------------|--------------------------------------------|--|--|--|

| VOLTAGE<br>(V) | DELAY TIME<br>50ms~200ms<br>(XC61H***1***-G) | DELAY TIME<br>80ms~400ms<br>(XC61H***4***-G) | DELAY TIME<br>1ms~50ms<br>(XC61H***5***-G) |  |  |  |

| X.0            | 0                                            | Α                                            | N                                          |  |  |  |

| X.1            | 1                                            | В                                            | Р                                          |  |  |  |

| X.2            | 2                                            | С                                            | R                                          |  |  |  |

| X.3            | 3                                            | D                                            | S                                          |  |  |  |

| X.4            | 4                                            | E                                            | Т                                          |  |  |  |

| X.5            | 5                                            | F                                            | U                                          |  |  |  |

| X.6            | 6                                            | Н                                            | V                                          |  |  |  |

| X.7            | 7                                            | K                                            | X                                          |  |  |  |

| X.8            | 8                                            | L                                            | Y                                          |  |  |  |

| X.9            | 9                                            | M                                            | Z                                          |  |  |  |

<sup>4</sup> represents production lot number

0 to 9, A to Z or inverted characters of 0 to 9, A to Z repeated.

(G, I, J, O, Q,W excluded)

<sup>\*</sup>No character inversion used.

- 1. The products and product specifications contained herein are subject to change without notice to improve performance characteristics. Consult us, or our representatives before use, to confirm that the information in this datasheet is up to date.

- 2. We assume no responsibility for any infringement of patents, patent rights, or other rights arising from the use of any information and circuitry in this datasheet.

- 3. Please ensure suitable shipping controls (including fail-safe designs and aging protection) are in force for equipment employing products listed in this datasheet.

- 4. The products in this datasheet are not developed, designed, or approved for use with such equipment whose failure of malfunction can be reasonably expected to directly endanger the life of, or cause significant injury to, the user.

- (e.g. Atomic energy; aerospace; transport; combustion and associated safety equipment thereof.)

- Please use the products listed in this datasheet within the specified ranges.

Should you wish to use the products under conditions exceeding the specifications, please consult us or our representatives.

- 6. We assume no responsibility for damage or loss due to abnormal use.

- 7. All rights reserved. No part of this datasheet may be copied or reproduced without the prior permission of TOREX SEMICONDUCTOR LTD.

TOREX SEMICONDUCTOR LTD.